Institut Mines-Telecom

# Virtual Prototyping from SysML Models

#### **Presentation and Demonstrations**

Ludovic Apvrille ludovic.apvrille@telecom-paristech.fr

Journée SysML France

Virtual prototyping in a nutshell

#### Partitioning with DIPLODOCUS Methodology

Deployment with AVATAR Virtual prototyping from design models Customizing code generation in TTool

#### Virtual prototyping in a nutshell

Partitioning with DIPLODOCUS

Deployment with AVATAR

3/42 06/02/2014 Institut Mines-Telecom

#### Definition

#### Generic definition

- From greek:  $\pi \rho \omega \tau \sigma \tau u \tau \sigma v$

- A prototype is an early sample, model or release of a product built to test a concept or process or to act as a thing to be replicated or learned from (Wikipedia)

#### In our context

- Prototyping = experimenting a functional model mapped onto a concrete hardware architecture

- Virtual prototyping = experimenting a functional model mapped onto a hardware model

- ► Hardware model can be more or less abstract/concrete

- Example : CPUs emulated with Instruction Set Simulator, abstract instructions, etc.

#### **Abstraction Level**

#### HOW TO CREATE A STABLE DATA MODEL

(Source: Peek and Poke, July, 2013)

5/42 06/02/2014 Institut Mines-Telecom

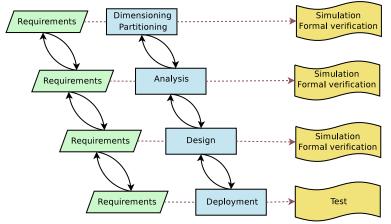

# Developing an Embedded System: Methodology and Abstraction levels

## Virtual Prototyping at Two Abstraction Levels

#### Partitioning

- Hardware highly abstracted

- Goal: Analyzing various functionally equivalent implementation alternatives

- Mapping of functions and communications

- Metrics:

- CPU load

- Bus occupation

- Silicon area

#### Deployment

- Functions to be software-implemented have been designed

- Hardware target is not yet available

- Or not easy/practical to use

- Goal: Determining precise timing and control issues

- Scheduling policy

- Latencies

- Missed deadlines

# **TTool: A Multi Profile Platform**

#### TTool

- Open-source toolkit mainly developed by Telecom ParisTech / COMELEC

- Multi-profile toolkit

- DIPLODOCUS, AVATAR, ...

- Support from academic (e.g. INRIA, ISAE) and industrial partners (e.g., Freescale)

#### Main ideas

Lightweight, easy-to-use toolkit Simulation with model animation Formal proof at the push of a button

8/42 06/02/2014

Institut Mines-Telecom

Methodology

#### Virtual prototyping in a nutshell

#### Partitioning with DIPLODOCUS Methodology

Deployment with AVATAR

9/42 06/02/2014 Institut Mines-Telecom

Methodology

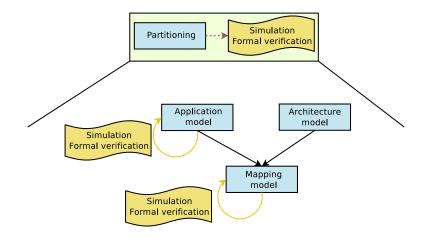

# **DIPLODOCUS** in a Nutshell

#### DIPLODOCUS = UML Profile

- System-level Design Space Exploration

- Y-Methodology

#### Main features

- High level of abstraction

- Exchanged data are unvalued

- Complexity operator

- Parametrized hardware nodes

- Formal semantics

- Very fast simulation support

Methodology

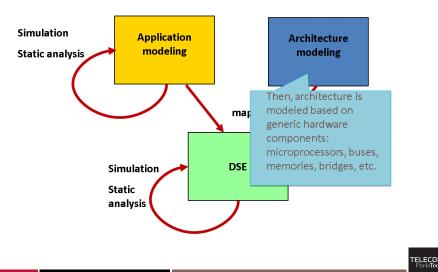

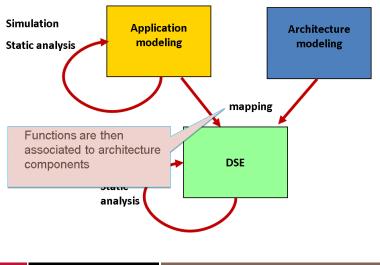

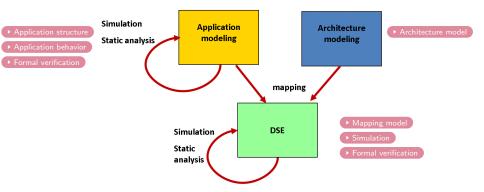

## Partitioning with the Y-Methododology

Methodology

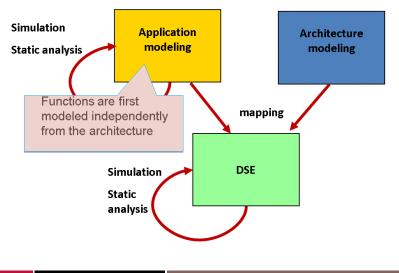

# **Application Modeling**

ELECU

Methodology

#### **Architecture Modeling**

Methodology

#### Mapping

ELECOM ParisTect

Methodology

## Browsing the DIPLODOCUS Methodoology

Methodology

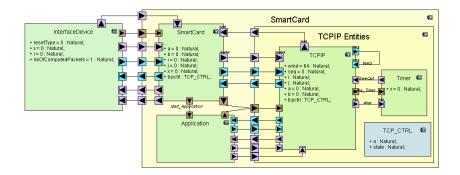

#### Application Structure (Smart Card system)

Methodology

## **Application Behavior**

Activity Diagram of the SmartCard component

# Formal Verification at Application Level

- No assumption on the underlying architecture

- ► All possible interleavings between actions are considered

- ► Formal verification is based on LOTOS/CADP or UPPAAL

- Press-button approach

Reachability of: Wait event: data\_Ready\_SC() -> property is satisfied

Liveness of: Wait event: data\_Ready\_SC() -> property is NOT satisfied

#### 18/42 06/02/2014 Institut Mines-Telecom

Methodology

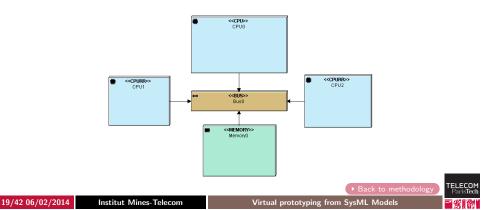

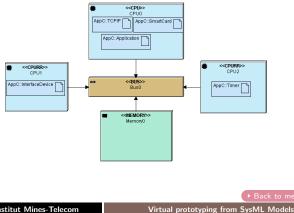

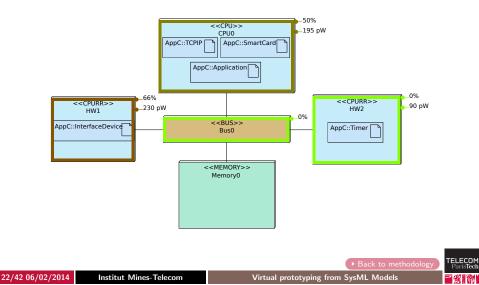

#### Architecture

- Given in terms of parameterized nodes

- ► CPU, HWA, Bus, Memory, Bridge, etc.

- CPU parameters: scheduling policy, cache miss ratio, miss-branching prediction, pipeline size, etc.

Methodology

# Mapping

- Task are mapped on execution nodes (e.g., CPUs, HWAs)

- Channels are mapped on communication and storage nodes

Methodology

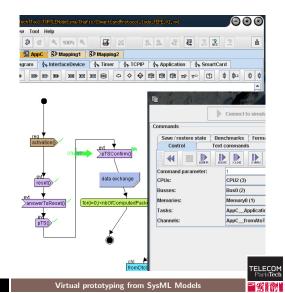

# After-Mapping Simulation

- TTool Built-in simulator

- Extremely fast

- Diagram animation

- Step-by-step execution, breakpoints, etc.

Methodology

# After-Mapping Simulation (Cont.)

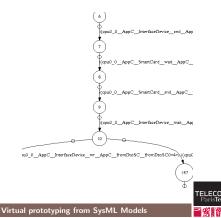

# **After-Mapping Formal Verification**

- TTool built-in simulator can compute all possible execution paths

- Graph analysis and visualization

| Analysis on the los O Deadlocks O Shortest Pat |    | ongest Paths                           |  |  |  |

|------------------------------------------------|----|----------------------------------------|--|--|--|

| General info.                                  |    | Statistics                             |  |  |  |

| Transition                                     | Nb |                                        |  |  |  |

| allCPUsTerminated<24>                          | 1  | (176, 177)                             |  |  |  |

| allCPUsTerminated<26>                          | 1  | (172, 173)                             |  |  |  |

| allCPUsTerminated<38>                          | 4  | (81, 82), (98, 99), (115, 116)         |  |  |  |

| allCPUsTerminated<40>                          | 4  | (77, 78), (94, 95), (111, 112)         |  |  |  |

| allCPUsTerminated<43>                          | 1  | (64, 65)                               |  |  |  |

| allCPUsTerminated<45>                          | 1  | (60, 61)                               |  |  |  |

| allCPUsTerminated<47>                          | 1  | (138, 139)                             |  |  |  |

| allCPUsTerminated<49>                          | 1  | (134, 135)                             |  |  |  |

| allCPUsTerminated<53>                          | 1  | (47, 48)                               |  |  |  |

| allCPUsTerminated<55>                          | 1  | (43, 44)                               |  |  |  |

| cpu0_0AppCApplicationsn                        | 8  | (46, 47), (63, 64), (80, 81), (9       |  |  |  |

| cpu0_0AppCApplicationsn                        | 8  | (40, 41), (57, 58), (74, 75), (9       |  |  |  |

| cpu0_0AppCApplicationsn                        | 8  | (33, 34), (50, 51), (67, 68), (8       |  |  |  |

| cpu0_0AppCApplicationsn                        | 8  | (37, 38), (54, 55), (71, 72), (8       |  |  |  |

| cpu0_0AppCApplicationwa                        | 8  | (32, 33), (49, 50), (66, 67), (8       |  |  |  |

| cpu0_0_AppC_Application_wr                     |    | (36, 37), (53, 54), (70, 71), (8       |  |  |  |

| cpu0_0AppCInterfaceDevice                      | 1  | (10, 157)                              |  |  |  |

| cpu0_0AppCInterfaceDevice                      | 1  | (0, 1)                                 |  |  |  |

|                                                |    | •••••••••••••••••••••••••••••••••••••• |  |  |  |

| Close                                          |    |                                        |  |  |  |

Methodology

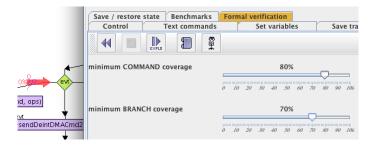

# After-Mapping Coverage-Enhanced Simulation

Possibility to select a given part of the model to be explored

- Minimum percentage of operators coverage

- Minimum percentage of branch coverage

Implementation: TTool built-in model-checking techniques

ELECO

Methodology

#### A Few Case Studies ...

- MPEG coders and decoders (Texas Instruments)

- LTE SoC (Freescale)

- Partitioning in vehicle embedded systems (EVITA project)

- Partitioning and code generation for Software-Defined Radio systems (SACRA project)

Virtual prototyping from design models Customizing code generation in TTool

# Outline

Virtual prototyping in a nutshell

Partitioning with DIPLODOCUS

#### Deployment with AVATAR

Virtual prototyping from design models Customizing code generation in TTool

Virtual prototyping from design models Customizing code generation in TTool

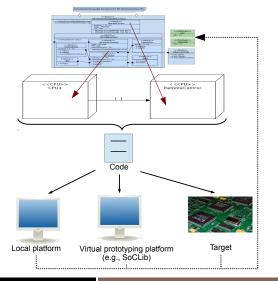

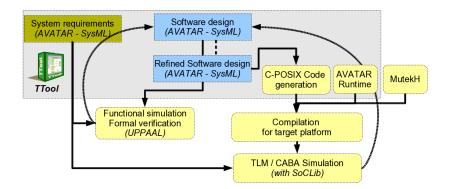

# **Deployment: Overview**

Virtual prototyping from design models Customizing code generation in TTool

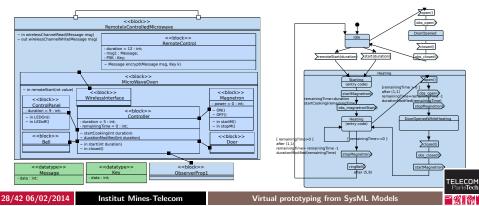

# **AVATAR** Design

- Block Definition and Internal Block diagrams are merged

- Synchronous and asynchronous communications

- Interactive simulation

- Formal verification of safety and security properties

# Principle of Code Generation

- Only AVATAR design diagrams are taken into account

- Generated code relies on POSIX threads

- One thread per block

- Synchronous communications between blocks is implemented in the AVATAR runtime with POSIX mutex

- Asynchronous communications relies on linked lists managed in the AVATAR runtime

- Time is handled based on POSIX clock\_gettime() with CLOCK\_REALTIME option

....

Virtual prototyping from design models Customizing code generation in TTool

#### Method

# Steps

- 1. Model refinement

- 2. Selection of an OS, setting of options of this OS (scheduling algorithm, ...)

- 3. Selection of a hardware platform, and selection of a task allocation scheme

- 4. Code generation (press-button approach)

- 5. Manual code improvement Code might also be manually added at model level

- 6. Code compilation and linkage with OS

- 7. Simulation platform boots the OS and executes the code

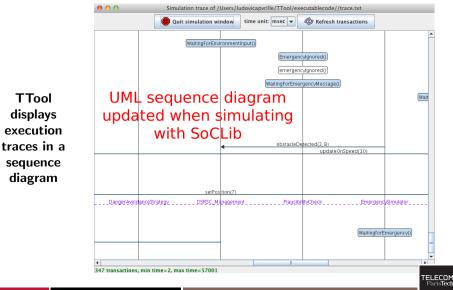

- 8. Execution analysis: directly in TTool (sequence diagram) or with debuggers (e.g., *gdb*)

Virtual prototyping from design models Customizing code generation in TTool

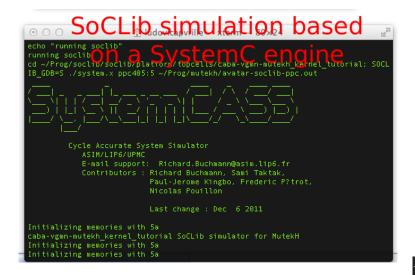

# Support: SoCLib and MutekH

#### Hardware platform simulator: SoCLib (www.soclib.fr)

- Virtual prototyping of complex Systems-on-Chip

- Supports several models of processors, buses, memories

- Example of CPUs: MIPS, ARM, SPARC, Nios2, PowerPC

- Two sets of simulation models:

- TLM = Transaction Level Modeling

- CABA = Cycle Accurate Bit Accurate

Embedded Operating System: MutekH (www.mutekh.fr)

- Natively handles heterogeneous multiprocessor platforms

- POSIX threads support

- Note: any Operating System supporting POSIX threading and that can be compiled for SoCLib could be used

Virtual prototyping from design models Customizing code generation in TTool

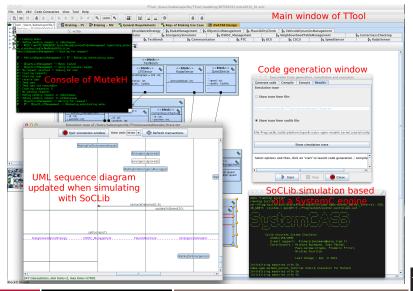

#### **Graphical Environment**

33/42 06/02/2014

Institut Mines-Telecom

Virtual prototyping from SysML Models

TELECO

Virtual prototyping from design models Customizing code generation in TTool

# (Virtual) Prototyping: Code Generation

| • • • • Executable Code generation, compilation and execution                                 |  |  |  |  |

|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Generate code Compile Execute Results                                                         |  |  |  |  |

| Code generation                                                                               |  |  |  |  |

| Base directory of code generation code:                                                       |  |  |  |  |

| /Users/ludovicapvrille/TTool/executablecode/                                                  |  |  |  |  |

| 🗹 Remove .c / .h files                                                                        |  |  |  |  |

| ✓ Remove .x files                                                                             |  |  |  |  |

| Put debug information in generated code                                                       |  |  |  |  |

| ✓ Put tracing capabilities in generated code                                                  |  |  |  |  |

| ✓ Optimize code                                                                               |  |  |  |  |

| 1 time unit =                                                                                 |  |  |  |  |

| sec 💌                                                                                         |  |  |  |  |

| Code generator used:                                                                          |  |  |  |  |

| AVATAR CPOSIX                                                                                 |  |  |  |  |

|                                                                                               |  |  |  |  |

| Select options and then, click on 'start' to launch code generation / compilation / execution |  |  |  |  |

|                                                                                               |  |  |  |  |

|                                                                                               |  |  |  |  |

|                                                                                               |  |  |  |  |

| Start Stop Close                                                                              |  |  |  |  |

EI ECO

Virtual prototyping from design models Customizing code generation in TTool

# Virtual Prototyping: SocLib Simulation

35/42 06/02/2014 Institut Mines-Telecom

Virtual prototyping from design models Customizing code generation in TTool

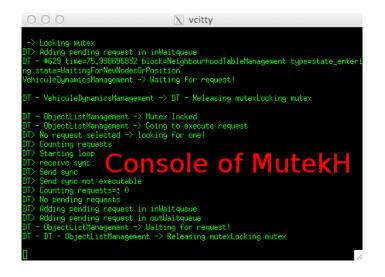

## Virtual Prototyping: Console

Virtual prototyping from design models Customizing code generation in TTool

# (Virtual) Prototyping: Trace

Virtual prototyping from design models Customizing code generation in TTool

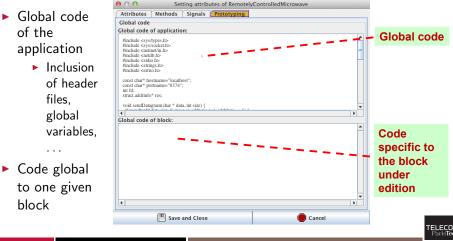

# **Customizing Generated Code with Your Own Code: Application and Block Code**

38/42 06/02/2014 Institut Mines-Telecom

ELECU

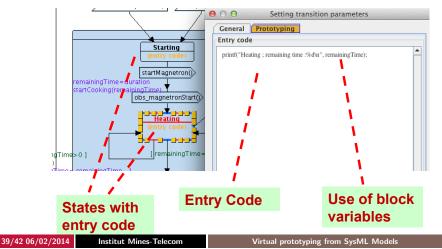

# **Customizing Generated Code with Your Own Code: State Entry Code**

#### Code executed whenever a state is reached

Virtual prototyping from design models Customizing code generation in TTool

# Use of Customized Generated Code

#### Console debug

Using e.g. printf() function

#### Connection to a graphical interface

- Piloting the code with a graphical interface

- Visualizing what's happening in the executed code

- Connection to graphical interface via, e.g., *sockets*

Virtual prototyping from design models Customizing code generation in TTool

# Use of Customized Generated Code (Cont)

#### Graphical interface for the microwave oven

41/42 (

Socket connection to a graphical interface programmed in Java

|                                                                                                           | 000           | Microwave demonstration       |                      |

|-----------------------------------------------------------------------------------------------------------|---------------|-------------------------------|----------------------|

| OOO Executable Code generation, compilation and execution                                                 |               |                               |                      |

| Generate code Compile Execute Results                                                                     | ]             |                               |                      |

| Execution                                                                                                 |               |                               |                      |

| ⊖ Run code:                                                                                               |               |                               |                      |

| /Users/ludovicapvrille/TTool/executablecode/run.x                                                         | <u> </u>      |                               | 1                    |

| Run code and trace events (if enabled at code generation):                                                | on)           |                               |                      |

| rool/executablecode/run.x /Users/ludovicapvrille/TTool/executablecode//trace.txt                          | ting          |                               | Cooking              |

| ○ Run code in soclib / mutekh:                                                                            |               |                               |                      |

| make -C /Users/ludovicapvrille/TTool/executablecode runsoclib                                             | nem:<br>ifter |                               |                      |

|                                                                                                           | ema<br>Jurat  |                               |                      |

| Select options and then, click on 'start' to launch code generation / compila                             |               |                               |                      |

| Executing code with command:<br>/Users/ludovicapvrille/TTool/executablecode/run.x /Users/ludovicapvrille/ |               |                               |                      |

| I I I I I I I I I I I I I I I I I I I                                                                     |               |                               |                      |

| Start Stop Close                                                                                          | 1             |                               |                      |

| remainingTime = remainingTime -1                                                                          |               |                               |                      |

| durationModified(remainingTime) stopMagnetron()                                                           |               |                               |                      |

|                                                                                                           |               |                               |                      |

| ringBell(                                                                                                 |               | -                             |                      |

| after (5,9)                                                                                               |               |                               | TELECOM<br>ParisTect |

| /02/2014 Institut Mines-Telecom                                                                           | Virtua        | prototyping from SysML Models |                      |

Virtual prototyping from design models Customizing code generation in TTool

#### To Go Further ...

# Viplodocus

#### TTool, DIPLODOCUS, AVATAR

ttool.telecom-paristech.fr